# Design and Implementation of Millimeter-Wave Power Amplifiers on CMOS

presented by

Byron Neil Wicks

BE(Hons)(Elec)(Melb) BSc(Math)(Melb)

Submitted in total fulfilment of the requirements of the degree of

# **Doctor of Philosophy**

National Information and Communication Technology Australia

Department of Electrical & Electronic Engineering

The University of Melbourne

Australia

January, 2009

Dedicated to my family, friends, and teachers, thank you.

#### **Abstract**

This thesis develops the theory and design techniques used to implement Complementary Metal–Oxide–Semiconductor (CMOS) millimetre-wave power amplifiers for use in integrated wireless transceivers allowing low cost, power efficient, high data rate and highly integrated transceivers for communication and radar applications.

Although technology is constantly improving and knowledge is continually advancing the full integration of a power amplifier on die remains a challenge for millimetre wave transceivers. This is due to several causes: the reduction in supply voltage with the scaling of CMOS technology; the limited power gain of the active devices at millimetre-wave frequencies; and the high parasitic losses of the submicron CMOS process.

From the theory developed in this thesis several power amplifiers have been designed, implemented and tested including a millimeter-wave automotive power amplifier, a 75-95 GHz wideband power amplifier and a 60-GHz Doherty power amplifier.

#### **Declaration**

## This is to certify that

- (i) This thesis comprises only my original work towards the PhD,

- (ii) Due acknowledgement has been made in the text to all other material used,

- (iii) This thesis is less than 100,000 words in length, exclusive of tables, maps, bibliographies and appendices.

Byron Neil Wicks, January, 2009

#### Acknowledgement

This dissertation would not have been possible without the support of a great many people throughout my education, whether explicitly mentioned here or not, and to these people I am indebted.

First and foremost, I would like to thank my advisors: Professor Mareels for his invaluable advice and support over the years, for introducing me to the idea of what a research project entails and for his guidance throughout the process; Professor Skafidas and Professor Evans whose advice on technical matters was invaluable, and their guidance both on my individual project and the larger GiFi transceiver project was critical to the project's success.

To my fellow GiFi students, this work could not have been completed without your significant input and assistance. Thank you for the countless hours of help on the design, layout and testing of the transceiver, listening to my questions, humouring some of my theories and for all the general banter you provided. You have helped stop the dam breaking open many years too soon, helped me find some room upon the hill, and stopped my head exploding with dark forebodings too, so thank you, Chien M. Ta, Frank Zhang, Wave Yang, Yuan Mo, Tom Wang, Yu Feng, Jerry Liu, Gordana Felic, Praveen Nadagouda, Tim Walsh and Luan Ismahil.

I'd also like to recognise a number of graduate students and fellows from outside my technical field, but who definitely added to my overall experience at the University of Melbourne. They include Sumith Choy, Elma O'Sullivan-Greene, Brian Krongold, Sam McLaughlin, Andrea Varsavsky, and Adrian Mancuso.

Finally, this PhD would have not been possible without the constant love and support of my family throughout the many obstacles encountered over the decade that I have spent as a tertiary student. Their help had been essential in the completion of not only this work but

all my endeavours. I would not be where I am today with out them, without their contributions and the foundation that they have provided throughout my life.

Funding for this work was provided by National ICT Australia. National ICT Australia is funded by the Australian Government's Department of Communications, Information Technology, and the Arts and the Australian Research Council through Backing Australia's Ability and the ICT Research Centre of Excellence programs.

## **Table of Contents**

| CHAPTER 1 INTRODUCTION                                                      | 1                              |

|-----------------------------------------------------------------------------|--------------------------------|

| 1.1 Motivation                                                              | 1                              |

| 1.2 Introduction to the Millimetre Wave Spectrum                            | 4                              |

| 1.3 OBJECTIVE                                                               | 5                              |

| 1.4 Contributions                                                           | 5                              |

| 1.5 Organisation                                                            | 8                              |

| CHAPTER 2 CMOS TECHNOLOGY FOR MILLIMETRE-WAVE                               | POWER                          |

| AMPLIFIERS                                                                  | 9                              |

| 2.1 Introduction                                                            | 9                              |

| 2.2 MOTIVATION                                                              |                                |

| 2.3 ACTIVE DEVICES                                                          | 11                             |

| 2.4 PASSIVES                                                                | 19                             |

| 2.5 CMOS FUTURE TRENDS                                                      | 20                             |

| 2.5 CMOS FUTURE TRENDS                                                      | <u>2</u> 0                     |

| 2.6 CONCLUSION                                                              |                                |

|                                                                             | 21                             |

| 2.6 CONCLUSION                                                              | POWER                          |

| 2.6 CONCLUSION  CHAPTER 3 FUNDAMENTALS OF RADIO FREQUENCY  AMPLIFIER DESIGN | POWER23                        |

| 2.6 CONCLUSION                                                              | POWER 23                       |

| 2.6 CONCLUSION                                                              | POWER232323                    |

| 2.6 CONCLUSION                                                              | POWER 23 23 24                 |

| 2.6 CONCLUSION                                                              | POWER2323232429                |

| 2.6 CONCLUSION                                                              | 21 POWER2323242934             |

| 2.6 CONCLUSION                                                              | 21 POWER232324293445           |

| 2.6 CONCLUSION                                                              | 21  POWER232324293445          |

| 2.6 CONCLUSION                                                              | 21  POWER23232429345465        |

| 2.6 CONCLUSION                                                              | POWER2323242934455465 POWER    |

| 2.6 CONCLUSION                                                              | 21 POWER23232429345465 POWER67 |

| 2.6 CONCLUSION                                                              | 21 POWER23232429344565 POWER67 |

| 4.3 DESIGN AND IMPLEMENTATION                         | 70    |

|-------------------------------------------------------|-------|

| 4.4 Fabrication and Results                           | 72    |

| 4.5 CONCLUSION                                        | 74    |

| CHAPTER 5 A 75 – 95 GHZ WIDEBAND CMOS POWER AMPLIFIER | 75    |

| 5.1 Introduction                                      | 75    |

| 5.2 Transistor Design                                 | 76    |

| 5.3 CIRCUIT DESIGN                                    | 78    |

| 5.4 Experimental Results                              | 79    |

| 5.5 CONCLUSION                                        | 81    |

| CHAPTER 6 A 60-GHZ FULLY-INTEGRATED DOHERTY           | POWER |

| AMPLIFIER                                             | 83    |

| 6.1 Introduction                                      | 83    |

| 6.2 Architecture and Circuit Description              | 84    |

| 6.3 EXPERIMENTAL RESULTS                              | 87    |

| 6.4 CONCLUSION                                        | 89    |

| CHAPTER 7 CONCLUSION                                  | 91    |

| 7.1 Thesis Conclusion                                 | 91    |

| 7.2 Future Work                                       | 92    |

| RIRI IOCRAPHV                                         | 95    |

# List of Figures

| FIGURE 1 – POSSIBLE VISIONS OF A 60-GHZ TRANSCEIVER SOLUTION [27]                                        | 2   |

|----------------------------------------------------------------------------------------------------------|-----|

| FIGURE 2 – THE UNITED STATES (FCC) MILLIMETRE WAVE SPECTRUM ALLOCATION                                   |     |

| BELOW 100 GHz.                                                                                           | 3   |

| Figure 3 – Power Attenuation by Frequency [79]                                                           | 4   |

| Figure 4 $ { m MOS}$ worldwide manufacturing capacity in 8-inch wafer equival                            | ENT |

| areas. [76]                                                                                              | 10  |

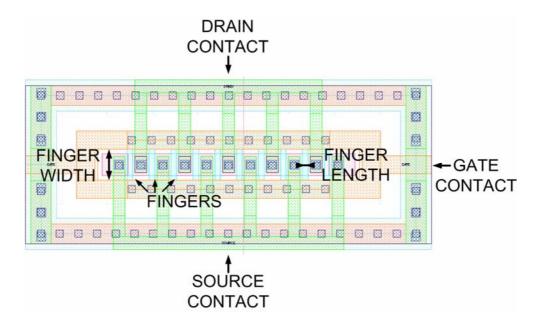

| Figure 5 – CAD layout of an NFET transistor with 8 fingers                                               | 11  |

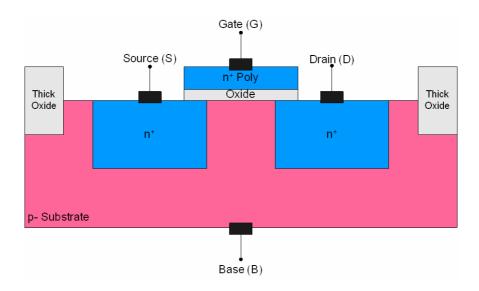

| Figure 6 – Structure of an NMOS Device                                                                   | 12  |

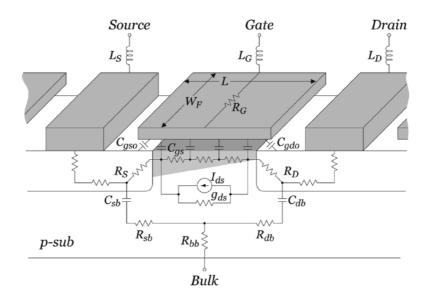

| Figure 7 – Simplified Physical Model of a single finger NMOS device. [18]                                | 13  |

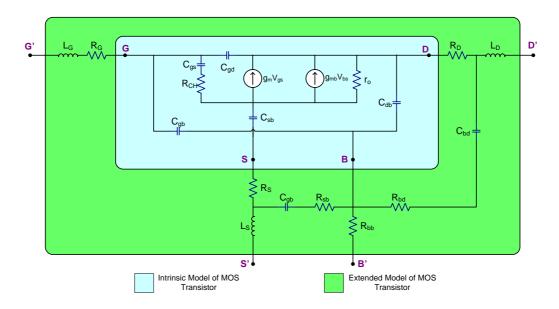

| FIGURE 8 – INTRINSIC MODEL AND EXTENDED MODEL OF A MOS DEVICE INCLUDING                                  |     |

| PARASITIC ELEMENTS                                                                                       | 13  |

| Figure 9 – NFET Characterisation Circuit                                                                 | 14  |

| Figure 10 – Simulations of $f_t$ of NMOS Transistor [94]                                                 | 15  |

| FIGURE 11 – SIMULATIONS OF F <sub>max</sub> OF NMOS Transistor                                           | 18  |

| FIGURE 12 – CROSS SECTION OF A MICROSTRIP TRANSMISSION LINE.                                             | 20  |

| Figure 13 – Cross section of a coplanar waveguide transmission line                                      | 20  |

| Figure 14 – Industry [40] estimates of future $f_{max}$ and $f_{\scriptscriptstyle T}$ transistor trends | 21  |

| Figure 15 – Industry [40] estimates of future transistor breakdown voltagi                               | E   |

| TRENDS.                                                                                                  | 21  |

| Figure 16 – Typical Homodyne Transmitter Architecture [53]                                               | 24  |

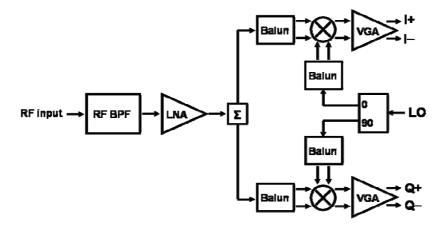

| Figure 17 – Typical Homodyne Receiver Architecture [53]                                                  | 24  |

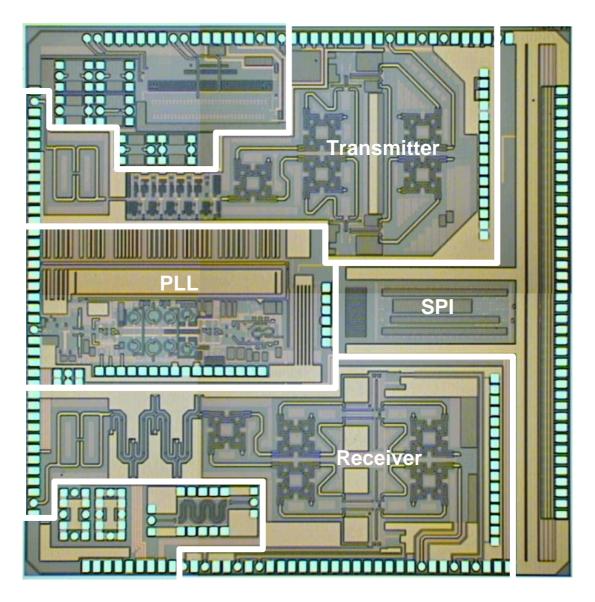

| Figure 18 – Single Chip 60GHz CMOS Transceiver Micrograph                                                | 25  |

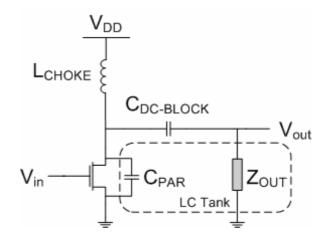

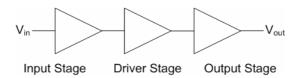

| Figure 19 – Genetic Power Amplifier Architecture                                                         | 26  |

| Figure 20 – Class D Architecture                                                                         | 27  |

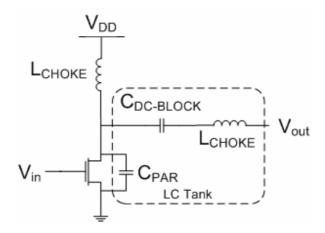

| Figure 21 – Class E Architecture                                                                         | 28  |

| Figure 22 – Class F Architecture                                                                         | 29  |

| FIGURE 23 – SHUNT PEAKED AMPLIFIER                                                                       | 30  |

| FIGURE 24 – EQUIVALENT MODEL OF THE SHUNT PEAKED AMPLIFIER                                               | 30  |

| FIGURE 25 – SHUNT AND SERIES PEAKED AMPLIFIER                                 | 31 |

|-------------------------------------------------------------------------------|----|

| Figure 26 – Amplifier with Tuned Load                                         | 31 |

| Figure 27 – Amplifier with Tuned Load Model                                   | 32 |

| FIGURE 28 – CASCODE AMPLIFIER WITH TUNED LOAD                                 | 33 |

| Figure 29 – Cascade Radio Architecture                                        | 34 |

| FIGURE 30 – TOTEM-POLE ARCHITECTURE                                           | 36 |

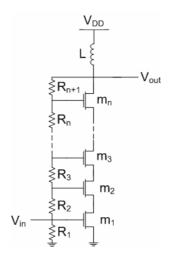

| FIGURE 31 – STACKED TRANSISTOR ARCHITECTURE                                   | 37 |

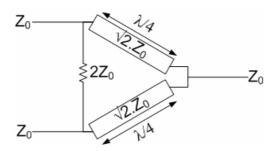

| FIGURE 32 – WILKINSON POWER COMBINER                                          | 37 |

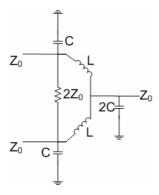

| FIGURE 33 – LUMPED ELEMENT WILKINSON POWER COMBINER                           | 38 |

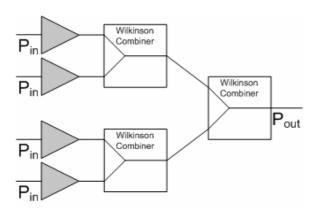

| FIGURE 34 – CORPORATE POWER COMBINER.                                         | 38 |

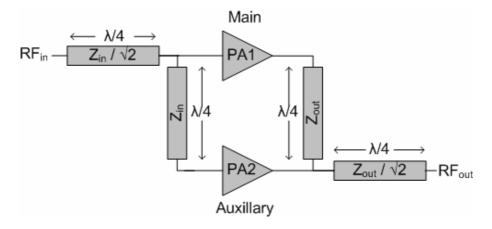

| FIGURE 35 – TWO AMPLIFIER DOHERTY AMPLIFIER ARCHITECTURE [95]                 | 39 |

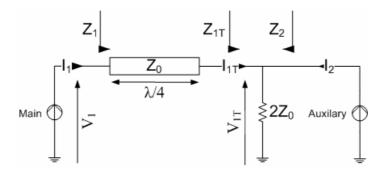

| FIGURE 36 – DOHERTY AMPLIFIER OUTPUT MODEL                                    | 40 |

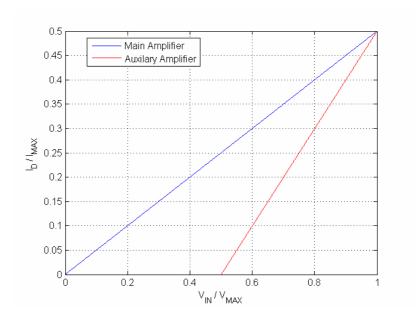

| Figure 37 – Doherty amplifier main and auxiliary device currents              | 43 |

| FIGURE 38 – DOHERTY AMPLIFIER MAIN AND AUXILIARY DEVICE VOLTAGES              | 43 |

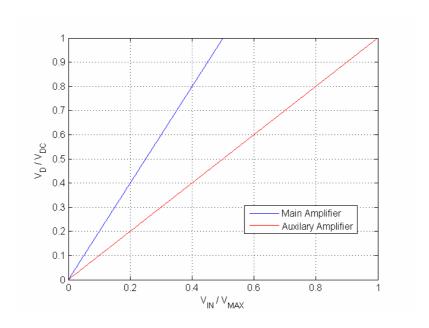

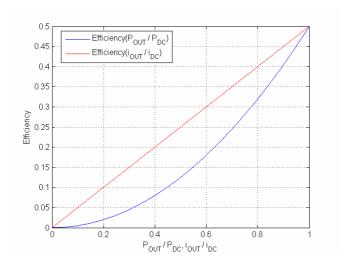

| FIGURE 39 – DOHERTY AMPLIFIER EFFICIENCY VERSUS POWER BACKOFF LEVEL           | 44 |

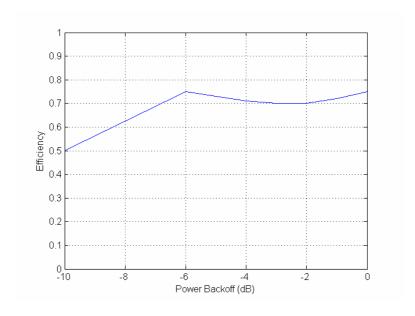

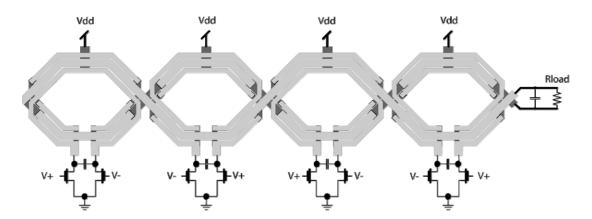

| Figure $40 - \text{Topology}$ of distributed active transformer [1]           | 44 |

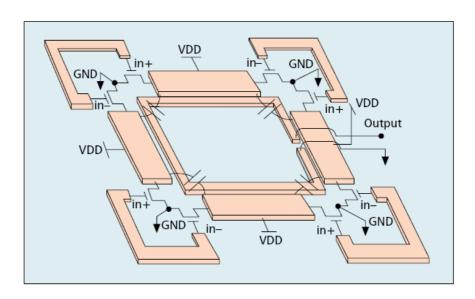

| FIGURE 41 – TOPOLOGY OF ON-CHIP TRANSFORMER [52]                              | 45 |

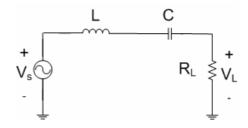

| FIGURE 42 – SERIES RLC CIRCUIT                                                | 45 |

| Figure 43 – Transfer Function of a Series RLC Circuit [61]                    | 47 |

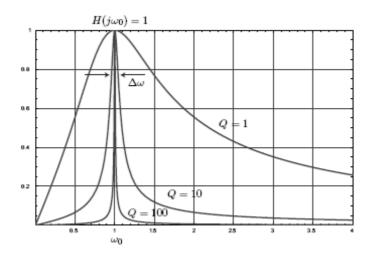

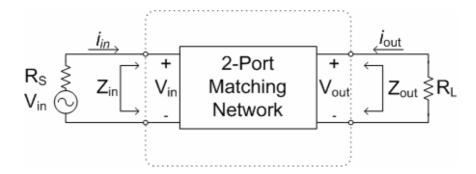

| FIGURE 44 – GENERIC 2-PORT MATCHING NETWORK                                   | 48 |

| FIGURE 45 – EXAMPLE OF A TYPICAL STABILITY RESPONSE                           | 51 |

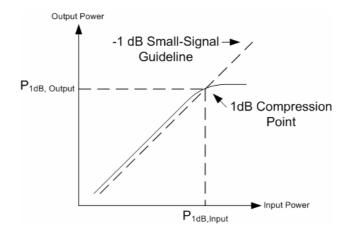

| Figure 46 – L-Matching Network[15]                                            | 53 |

| Figure 47 – PI-Matching Network                                               | 53 |

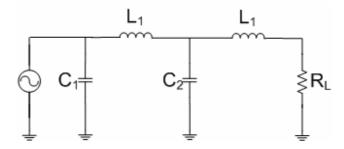

| FIGURE 48 – DEFINITION OF 1-DB COMPRESSION POINT.                             | 56 |

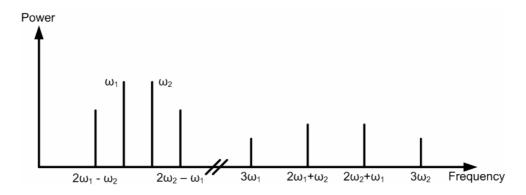

| Figure $49 - \text{The spectrum of the two-tone cubic intermodulation (IM3)}$ |    |

| PRODUCTS                                                                      | 57 |

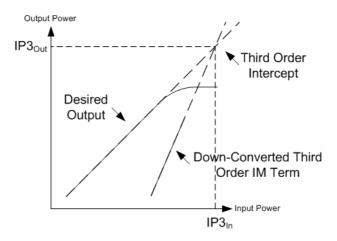

| FIGURE 50 – DEFINITION OF THIRD ORDER LINEARITY PARAMETERS.                   | 58 |

| Figure 51 – Amplitude Compression for Fundamental and $3^{\text{rd}}$ Order   |    |

| Intermodulation with 3 <sup>rd</sup> Order Intercept Point Marked [94]        | 59 |

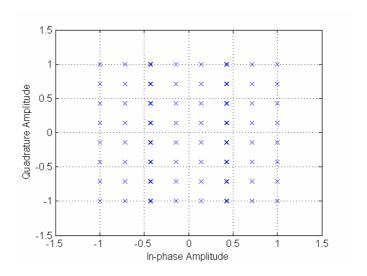

| FIGURE 52 – AN IDEAL 64-QAM CONSTELLATION.                                    | 59 |

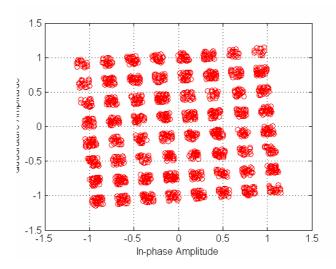

| FIGURE 53 – A 64-QAM CONSTELLATION WITH AM-AM AND AM-PM DISTORTION.           |    |

| FIGURE 54 – POWER EFFICIENCY OF CLASS A POWER AMPLIFIER REFERRED TO RATIO     | OF |

| POWER OUT TO POWER IN AND DRAIN CURRENT TO OUTPUT CURRENT                     | 64 |

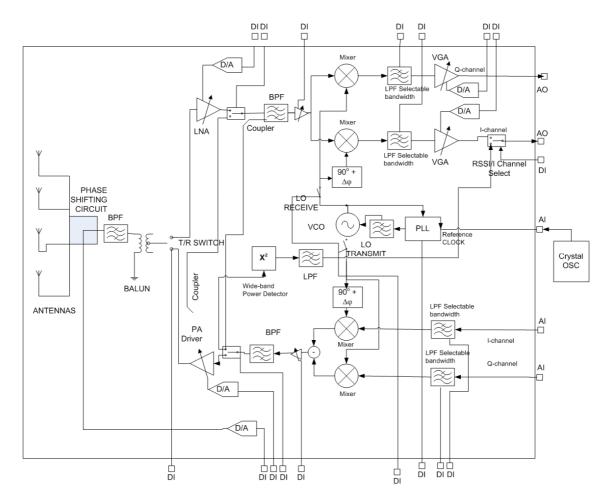

| FIGURE 55 – RADIO ARCHITECTURE ILLUSTRATING THE MAJOR COMPONENTS AND                                     |    |

|----------------------------------------------------------------------------------------------------------|----|

| FUNCTIONALITY OF THE RADAR ON A CHIP TRANSCEIVER. [94]                                                   | 69 |

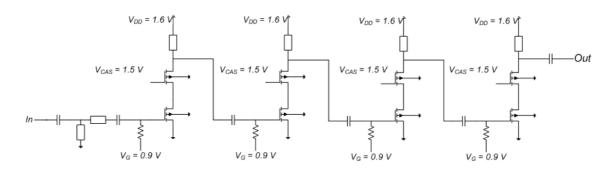

| Figure 56 – Simplified Schematic of 46.7-46.9 GHz 4-stage power amplifier                                |    |

| EMPLOYING TRANSMISSION LINES. [94]                                                                       | 70 |

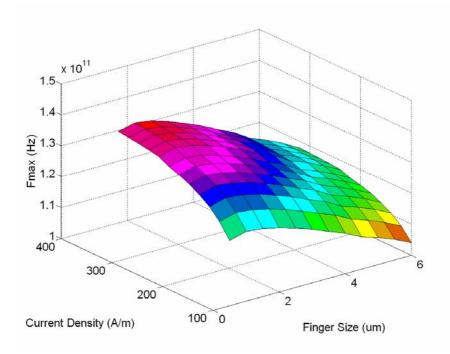

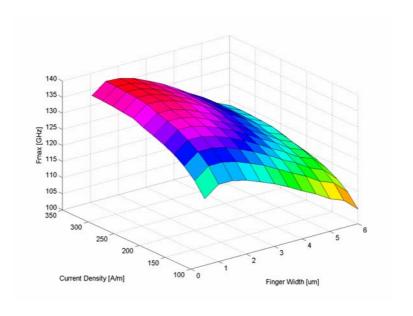

| Figure $57 - Simulated F_{max}$ for varying device finger size and current density.                      |    |

| Total device size was kept constant at 80 μm. [94]                                                       | 71 |

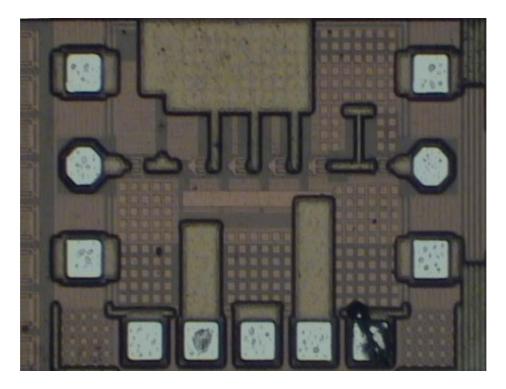

| FIGURE 58 – IMAGE OF FABRICATED POWER AMPLIFIER [94]                                                     | 72 |

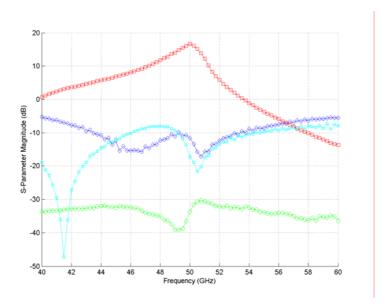

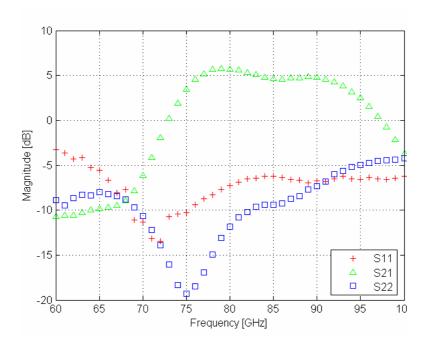

| Figure 59 – Measured S-parameters of PA in decibel scale [94]                                            | 73 |

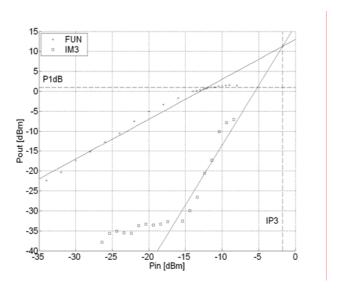

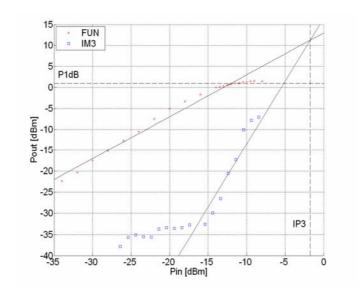

| Figure 60 – Two-tone distortion for the power amplifier showing $P_{\text{SAT}}$ , $P_{\text{1dB}}$ , IP |    |

| [94]                                                                                                     |    |

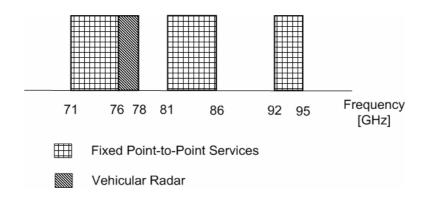

| FIGURE 61 – THE UNITED STATES FIXED POINT-TO-POINT AND RADAR BAND ALLOCATIO                              |    |

| IN THE 65 – 100 GHz spectrum 105[97]                                                                     | 75 |

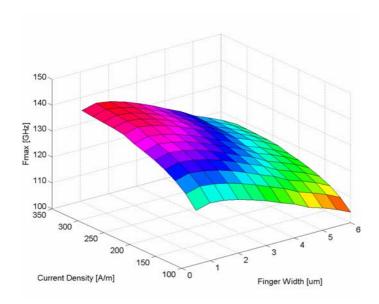

| $Figure\ 62-Simulated\ F_{max}\ For\ varying\ device\ finger\ size\ and\ current\ density.$              |    |

| Total device size was kept constant at 60 $\mu$ m [97]                                                   | 76 |

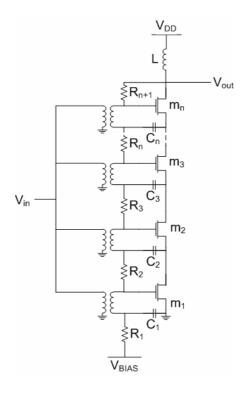

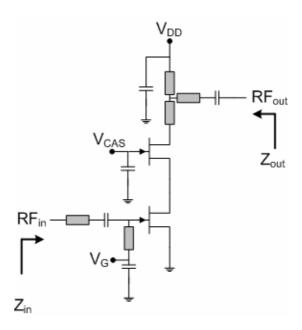

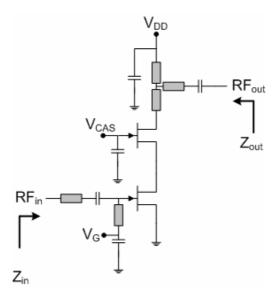

| FIGURE 63 – SCHEMATIC OF A SINGLE STAGE OF THE POWER AMPLIFIER [97]                                      | 77 |

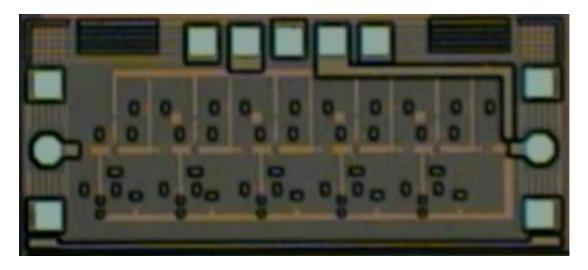

| Figure 64 – Die Micrograph of the 0.13 $\mu m$ CMOS 77-GHz PA with, dimensions                           |    |

| 1230 μM BY 520 μM [97]                                                                                   | 78 |

| Figure 65 – Measured S-parameters of the PA [97]                                                         | 79 |

| Figure 66 – Measured Large-signal Characteristics at 77 GHz [97]                                         | 80 |

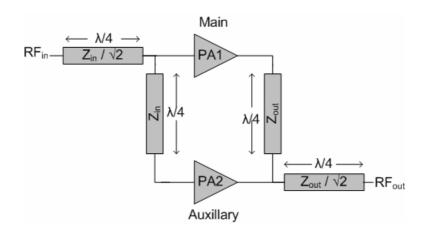

| Figure $67 - B$ lock diagram of the Doherty power amplifier configuration [95]                           | ]  |

|                                                                                                          | 83 |

| Figure $68 - Simulated F_{max}$ for varying device finger size and current density.                      |    |

| TOTAL DEVICE SIZE WAS KEPT CONSTANT AT 80 μM. [95]                                                       | 84 |

| Figure 69 – Schematic of a single stage of both the main and auxilliary                                  |    |

| AMPLIFIERS [95]                                                                                          | 85 |

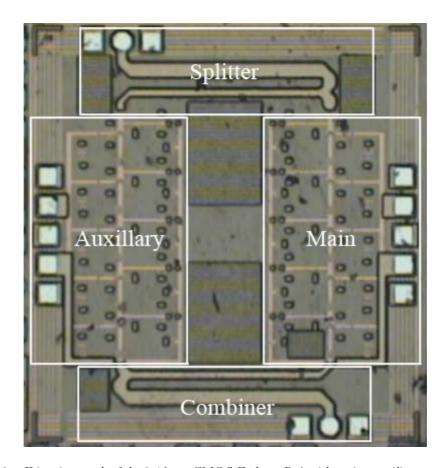

| Figure 70 – Die Micrograph of the $0.13\mu M$ CMOS Doherty PA with main,                                 |    |

| AUXILIARY AMPLIFIERS AND SPLITTERS LABELLED [95]                                                         | 86 |

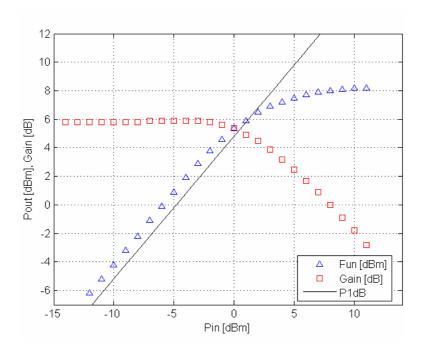

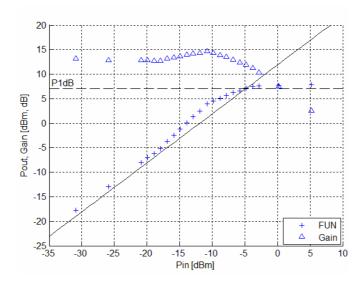

| FIGURE 71 – MEASURED RF PERFORMANCE OF THE DOHERTY PA AT 60 GHz [95]                                     | 88 |

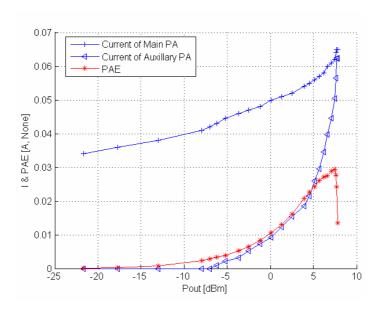

| Figure $72-$ Measured currents for both the main and auxiliary amplifiers ani                            | O  |

| EFFICIENCY OF THE DOHERTY PA [95]                                                                        | 89 |

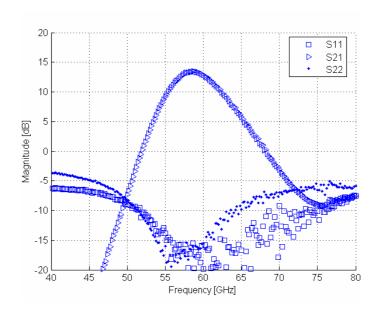

| FIGURE 73 – MEASURED S-PARAMETERS OF THE DOHERTY PA [95]                                                 | 89 |

|                                                                                                          |    |

## List of Tables

| TABLE I – SWEPT DEVICE PARAMETERS FOR NMOS TRANSISTOR                          | 15   |

|--------------------------------------------------------------------------------|------|

| Table II $-$ Comparison of the automotive amplifier with published mm-wave     |      |

| CMOS AMPLIFIERS                                                                | .74  |

| Table III – Comparison of the $75$ – $95$ GHz wideband CMOS power amplifier wi | ТН   |

| PUBLISHED CMOS MILLIMETER-WAVE PA RESULTS                                      | 81   |

| TABLE IV – COMPARISON OF THE DOHERTY PA WITH PUBLISHED CMOS MILLIMETER-        |      |

| WAVE PA RESULTS                                                                | . 90 |

# Chapter 1 Introduction

#### 1.1 Motivation

The continual advancement of Complementary Metal–Oxide–Semiconductor (CMOS) technology with Moore's Law has seen it consistently replacing more expensive exotic processes at centimeter wavelength frequencies, the portion of the spectrum ranging from 3-GHz to 30-GHz. As the CMOS process scales the transistors implemented in the process have increased in speed and are now able to operate in the millimeter wavelength frequencies, the portion of the spectrum ranging from 30-GHz to 300-GHz, and it is only a matter of time before CMOS becomes a viable alternative for millimeter wave applications.

The ability to implement transceivers in the millimetre wave spectrum with CMOS technology is set to be a boon to RF designers, allowing for new classes of cost efficient devices to be created. The motivation for this thesis originates from two of theses applications; high data rate wireless communication; and vehicular imaging.

#### 1.1.1 High Data Rate Wireless Communication

Consumers are demanding improved connectivity of their devices, including DVD players, portable games, digital cameras, digital audio and visual (A/V) players, personal computers, digital video recorders and high definition televisions (HDTVs), at high data rates, low cost and which connect seamlessly with minimal effort by the user. The millimetre wave spectrum promises to facilitate the realization of this vision, allowing users to connect between devices wirelessly and automatically.

A typical scenario for this technology is a consumer who visits a kiosk in a shopping centre and buys a movie, downloading it wirelessly to his portable A/V device. On returning home the portable A/V device would seamlessly connect to a HDTV, and surround sound system, turn them on automatically and play the rented movie. There would be no wires,

no switches or complex operating procedures required in order to be able to connect all of these devices.

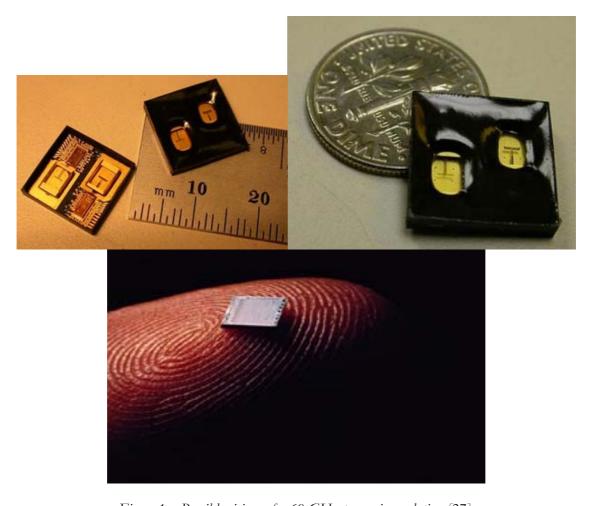

Figure 1 – Possible visions of a 60-GHz transceiver solution [27].

The Federal Communications Commission (FCC) and various international regulatory bodies have released up to 7 GHz of continuous bandwidth in the millimetre wave spectrum around the 60-GHz channel. This spectrum allocation is ideally suited to deliver the high data rate wireless communication services for both device connectivity and wireless personal area networks (WPAN).

#### 1.1.2 Vehicular Radar

Currently, automobile accidents are estimated to account for over 1.2 million fatalities and 50 million injuries annually [82]. There is now political pressure to reduce this carnage and the European Union and several countries are introducing targets to reduce road deaths by

50%. Studies [36] have shown that up to 50% of vehicle collisions could be avoided if vehicles were fitted with radar that assisted, with braking, lane departure and, driving in inclement weather. In order to facilitate the deployment of these technologies regulatory bodies including the FCC have allocated spectra at 24-29 GHz, 46.7-46.9 GHz and 76-78 GHz. Currently automotive radar systems are only equipped on luxury automobiles due to prohibitively high cost. In order for theses systems to be universally deployed across the entire price range of automobiles a low cost solution is urgently required.

#### 1.1.3 Cost Efficiency

Ultimately, for electronic devices, economic consideration decides the technology used in implementation and in order to achieve low costs with a high level of integration CMOS process technology is utilized. The CMOS process is the standard and most cost effective process for building digital circuits. Implementing radio frequency (RF) components of a device on CMOS would allow a high level of integration by combining the digital, mixed signal and RF components of the system to be integrated onto a single substrate allowing for a system-on-chip (SoC) or on a single package allowing for a system-in-a-package (SiaP). Transmitting at millimeter wave frequencies is also advantageous for the form factor of the antenna, as the size of the antenna is inversely proportional to the propagation frequency, and at millimeter wavelengths is in the order of millimeters enabling new packing options including integration of the antenna on the transceiver die, a feat not possible for current centimeter wave transceivers.

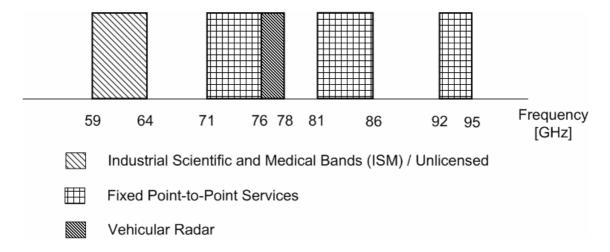

Figure 2 – The United States (FCC) millimetre wave spectrum allocation below 100 GHz.

Unfortunately, the CMOS process is inferior in terms of noise, power handling, substrate and coupling loss and transistor cut-off frequency to the more expensive silicon and type III-V element compounds such as Silicon Germanium (SiGe), Indium Phosphide (InP) and Gallium Arsenide (GaAs), traditionally used to implement millimeter-wave devices. As CMOS was designed primarily for the implementation of digital circuits, it is thus optimized for their implementation. Compared to these more traditional RF processes CMOS has greater process variability, lower carrier mobility and lower device breakdown voltages that pose challenges to the RF designer.

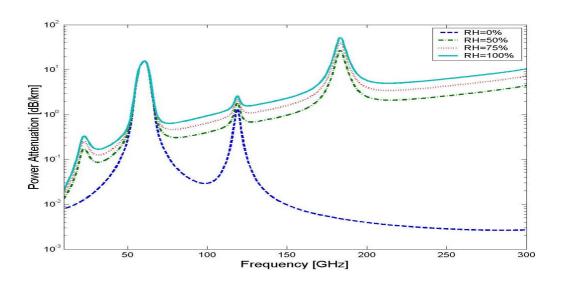

Figure 3 – Power Attenuation by Frequency [79]

#### 1.2 Introduction to the Millimetre Wave Spectrum

Designing a transceiver for operation in the millimeter wave spectrum gives rise to a unique set of advantages and challenges. The millimeter wave channel has high path attenuation, as shown in Figure 3, due to the signal being absorbed by the oxygen molecules in the air and higher attenuation due to walls and floors. In the 60-GHz region of the spectrum this attenuation is severe and limits the range of any device that employs the 60GHz frequency to approximately 20 meters or a single room. This is in contrast to various other wireless local area network (WLAN) technologies, such as IEEE 802.11b/a/g, that utilize lower frequencies and allow for greater range. Far from being a drawback, the large attenuation experienced by devices in the millimeter wave spectrum serves as an advantage for WPANs by increasing security, reducing interference from other wireless sources and allowing more

WPANs to occupy the same building. As a consequence of the attenuation the FCC regulations [25] allow a significantly more powerful signal to be transmitted than with other consumer wireless regulations.

#### 1.3 Objective

The objectives of this thesis focus on the implementation of millimeter wave power amplifiers (PAs) in 130-nm CMOS technology and their integration into millimeter wave transceivers.

A power amplifier is a circuit for increasing the current, voltage and power of a signal by harnessing supplementary power from a power supply and producing a significant output signal with one or more power amplifiers located on the transmit path of a transceiver. Each power amplifier has a unique set of requirements, including frequency, bandwidth, efficiency, linearity and cost, as dictated by the target application.

#### 1.4 Contributions

This thesis develops the theory and design techniques used to implement CMOS millimeter-wave power amplifiers and facilitates the development of low cost, power efficient, high data rate and highly integrated transceivers for WPAN and automotive radar applications. Although process technology is constantly improving and knowledge is continually advancing the full integration of a power amplifier on die remains a challenge for millimeter wave transceivers. This is due to several causes: the reduction in supply voltage with the scaling of CMOS technology; the limited power gain of the active devices at millimetre-wave frequencies; and the high parasitic losses of the submicron CMOS process.

The potential for single chip CMOS millimeter-wave transceivers for automotive radar applications is explored in chapter four. In this chapter a CMOS millimeter-wave integrated circuit (MMIC) power amplifier (PA) is designed and implemented for automotive radar applications with the purpose of system-on-chip integration with the rest of the electronics. To the best of the author's knowledge, this is the first reported fully integrated millimetre wave CMOS power amplifier focusing on automotive applications.

The feasibility of the use of CMOS technology for use in 71 - 76 GHz, 81 - 86 GHz and 92 - 95 GHz point-to-point link bands and the 77-GHz vehicular radar band is explored in chapter five. With a 75 - 95 GHz wideband power amplifier (PA) in 0.13- $\mu$ m CMOS implemented. To the best of the author's knowledge, this is the highest reported fully integrated millimetre wave CMOS power amplifier.

A Doherty amplifier is discussed in chapter six. To the best of the author's knowledge, this is the first reported fully integrated millimetre wave CMOS power amplifier employing the Doherty technique. It is able to transmit high power with improved average efficiency. The significance of the this work is that, it proves fully integrated CMOS millimetre-wave amplifiers are feasible and will continue to be feasible as the technology scales, it shows the Doherty technique is applicable to millimetre wave amplifiers allowing for improved efficiency especially the active load pull advantages, it demonstrates the high level of linearity required for millimetre wave devices such as high data rate transceivers, that imaging can be achieved with CMOS in the millimetre wave spectrum, and it shows that the issues of limited power generation and amplification at millimeter wave frequencies can be overcome.

The awards arising from this thesis include:

Best student paper for:

B. N. Wicks, C. M. Ta, E. Skafidas, R. J. Evans, and I. Mareels, "A 60-GHz Power Amplifier and Transmit/Receive Switch for Integrated CMOS Wireless Transceivers," The 2008 International Conference on Microwave and Millimeter Wave Technology (ICMMT 2008), Nanjing, P. R. China, April 21-24, 2008.

The publications arising from this thesis:

B. N. Wicks, E. Skafidas, R. J. Evans, and I. Mareels, "A 75 – 95 GHz Wideband CMOS Power Amplifier," The European Microwave Integrated Circuits Conference 2008, Amsterdam, 27-28 October 2008.

- B. Wicks, E. Skafidas, R. Evans, "A 60-GHz Fully-Integrated Doherty Power Amplifier Based on 0.13-μm CMOS," IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, June, 2008.

- B. N. Wicks, C. M. Ta, E. Skafidas, R. J. Evans, and I. Mareels, "A 60-GHz Power Amplifier and Transmit/Receive Switch for Integrated CMOS Wireless Transceivers," The 2008 International Conference on Microwave and Millimeter Wave Technology (ICMMT 2008), Nanjing, P. R. China, April 21-24, 2008.

- B. Wicks, E. Skafidas, I Mareels, R Evans, "A 46.7-46.9-GHz CMOS MMIC Power Amplifier for Automotive Radar Applications," IASTED Antennas, Radar and Wave Propagation (ARP 2008), 30 May–1 June 2007, pp 80 84.

- B. Wicks, R. J. Evans, and E. Skafidas, "Issues in the Implementation of a 60GHz Power Amplifier based on a 0.13-um CMOS Process for use in a WPAN integrated Transceiver," IEEE Power Amplifier Symposium, Orlando, USA, 21-22 Jan., 2008.

- F. Zhang, E. Skafidas, W. Shieh, B. Yang, B. N. Wicks and Z. Liu, "A 60-GHz Double-Balanced Mixer for Direct Up-Conversion Transmitter on 130-nm CMOS," 2008 IEEE Compound Semiconductor IC Symposium (CSICS).

- C. M. Ta, B. Wicks, F. Zhang, B. Yang, Y. Mo, K. Wang, Z. Liu, G. Felic, P. Nadagouda, T. Walsh, R. J. Evans, I. Mareels and E. Skafidas, "Issues in the Implementation of a 60GHz Transceiver on CMOS," The 2nd IEEE International Workshop on Radio-Frequency Integration Technology, Singapore, 09-11 Dec., 2007.

- B. N. Wicks, C. M. Ta, E. Skafidas, I. Mareels, and R. J. Evans, "A Transmit/Receive Switch and Power Amplifier on 130-nm CMOS for 60-GHz Wireless Transceiver," Melbourne Engineering Research Institute (MERIT), Melbourne, Australia, Nov. 22, 2007.

- B. Yang, Y. Mo, K. Wang, Y. Feng, B. Wicks, C. Ta-Minh, F. Zhang, Z. Liu, C. Liu, G. Felic, P. Nadagouda, T. Walsh, and E. Skafidas, "Implementation of a Gigabit Per Second Millimetre Wave Transceiver on CMOS," The 2<sup>nd</sup> International Conference on Wireless

Broadband and Ultra Wideband Communications, AusWireless 2007, 27-30 Aug., 2007, pp. 71-74.

B. Yang, Y. Mo, B. Wicks, C. Ta-Minh, F. Zhang, Z. Liu, G. Felic, K. Wang, C. Liu, P. Nadagouda, T. Walsh, R.J. Evans and E. Skafidas, "Implementation of a Gigabit per Second Millimeter Wave Transceiver on CMOS," AusWireless Book Chapter 2008.

#### 1.5 Organisation

The thesis consists of six chapters. Chapter two is an overview of the CMOS process that is utilised to implement the transceiver and highlights the strengths and weaknesses of this selection, the models used for passives and actives and their effect on the design of the power amplifiers. Also discussed is the impact future advances CMOS technology will have on the implementation of power amplifiers.

Chapter three presents the fundamentals concepts required for the design and implementation of a power amplifier (PA) in a radio frequency (RF) system, including an overview of the concepts of classes of PA, high frequency amplifier techniques, high power amplifier techniques, matching networks, linearity and efficiency will be discussed.

Chapter four explores the potential for single chip CMOS millimeter-wave transceivers for automotive radar applications. In this chapter a CMOS millimeter-wave integrated circuit (MMIC) power amplifier (PA) is designed for automotive radar applications with the intention of integration with the rest of the electronics is designed and implemented.

In chapter five a 75 – 95 GHz wideband power amplifier (PA) in 0.13-μm CMOS is implemented to explore the feasibility of low-cost CMOS technology for use in 71 – 76 GHz, 81 – 86 GHz and 92 – 95 GHz Industrial, Scientific and Medical (ISM) bands and the 77-GHz vehicular radar band.

In chapter six a sixty-gigahertz (60-GHz) Doherty power amplifier (PA) is been designed and implemented on 0.13 µm RF-CMOS for use in an integrated 60-GHz WPAN transceiver.

Chapter seven concludes the thesis and suggests the potential areas for future work.

# Chapter 2 CMOS Technology for Millimetre-Wave Power Amplifiers

#### 2.1 Introduction

Power Amplifiers have been implemented with numerous technologies since their inception. This chapter presents the motivation for the use of Silicon Complementary Metal–Oxide–Semiconductor (CMOS) technology and highlights the strengths and weaknesses of this selection, discusses implementation of the actives and passives and the impact of future technology advances.

#### 2.2 Motivation

When compared to the type III-V semiconductor technology that is traditionally utilised CMOS is found to be inferior in many measures. The performance metrics of the actives implemented in CMOS technology, whether maximum frequency of oscillation, frequency of transition or breakdown voltage, all tend to be significantly lower then the type III-V semiconductors. The high-resistive silicon substrate results in poorer isolation and higher parasitic losses in the passives. The two compelling reasons to consider CMOS technology, manufacturing cost and level of integration both contribute to reducing the overall cost of the device. These issues are discussed further in this section.

#### 2.2.1 Manufacturing Capacity

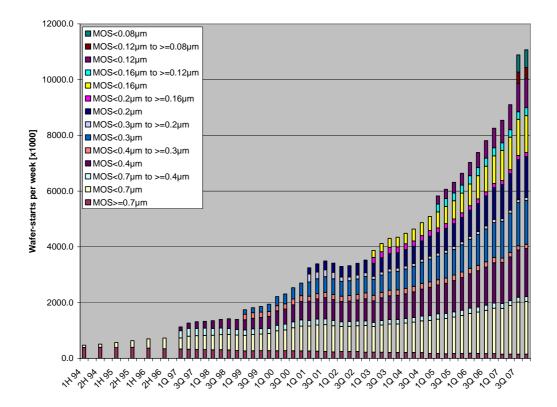

The ubiquity of CMOS semiconductors today has been facilitated by the continual reduction of chip fabrication costs. This reduction in cost has been achieved by the increase in wafer area, chip yields and quality assurance. *Figure 4* shows the magnitude of the increase in MOS manufacturing capacity (excluding BiCMOS only capacity) that has occurred over the previous 25 years. In this period MOS capacity has increased from almost 500 8-inch equivalent wafers every six months in 1994 to over 2000 8-inch equivalent wafers every 3 months in 2007, an increase of over 800% [77]. Industry groups [40], [76], [77] are predicting these trends to continue for at least the next decade.

Figure 4 – MOS worldwide manufacturing capacity in 8-inch wafer equivalent areas. [76]

#### 2.2.2 Level of Integration

In the manufacture of electronics higher integration equates to lower cost. The CMOS process is already the standard and most cost effective process for building digital circuits. The ability to implement the front-end radio frequency (RF) components of the transceiver on this process, instead of the more traditional type III-V semiconductor technology, enables a higher level of integration by allowing the combination of the digital, mixed signal and RF components of the system to be integrated onto a single substrate. Operating at millimetre wave frequencies reduces the dimensions of the antenna, to the order of millimeters, enabling new packing options including integration of the antenna on the transceiver die, a feat not possible for current centimeter wave transceivers. Ultimately this integration, and the resultant cost efficiency, would elevate CMOS to the process of choice for millimeter wave devices.

#### 2.3 Active Devices

This section describes the important active device concepts required to implement a millimetre-wave power amplifier including device parameters, inherent characteristics, device models, and figures of merit.

This section will concentrate on NMOS transistors as these are employed as the active building block in the design of the power amplifier. This is due to NMOS devices having higher gain than PMOS devices because of the higher mobility of electrons in silicon. As a consequence lower current densities are required, less power is dissipated and higher output power can be achieved.

#### 2.3.1 Device Parameters

NFET devices electrical performance varies with a number of parameters. It is the design engineer's role to optimise these parameters for each circuit. These parameters, shown in Figure 5, include: transistor width (W), the total effective width of the transistor; transistor finger length (L), the length; of each individual finger; number of finger (n), the total number of fingers in the transistor; transistor finger width (W<sub>F</sub>), the individual width of each transistor finger. The effects of these parameters on the performance of the device will be investigated below.

Figure 5 – CAD layout of an NFET transistor with 8 fingers.

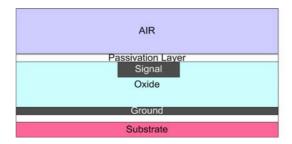

Figure 6 – Structure of an NMOS Device.

#### 2.3.2 Device Structure

Figure 6 shows a simplified cross sectional view of an NMOS device with the four terminals labelled: source, drain, gate and base. There are two n-well regions that are heavily doped by diffusing n-type impurities deep into the p-type substrate. A thick oxide region is grown outside the active areas in order to isolate each transistor. A gate terminal is formed by a heavily doped polysilicon, which is isolated from the substrate by a thin film of silicon dioxide. This creates *pn* junctions with the source and substrate, and the drain and substrate regions. In the area between the source and drain regions a conducting channel is built up under appropriate biasing conditions allowing current to flow. For further explanation of this process consult [50],[62],[65],[72],[92].

#### 2.3.3 Device Model

By taking into account all the parasitic capacitances, inductances and resistances it is possible to produce a physical model depicting the most significant loss mechanisms of CMOS devices as shown in Figure 7.

Extrapolating a small signal transistor model from the physical model produces a circuit model that can be used for simulations. It should be mentioned that this model infers that the high frequency performance is limited by resistive losses, the most significant being the

gate resistance ( $R_G$ ), series source/drain resistances ( $R_S$ ,  $R_D$ ), nonquasi-static channel resistance ( $R_{CH}$ ), and resistive substrate network ( $R_{sb}$ ,  $R_{bd}$  and  $R_{bb}$ ) [23], [24].

Figure 7 – Simplified Physical Model of a single finger NMOS device. [18]

Figure 8 – Intrinsic model and extended model of a MOS device including parasitic elements.

#### 2.3.4 Figures of Merit

The most significant figures of merit (FOM) for the frequency characteristics of active devices are the frequency of transition ( $f_t$ ), the maximum frequency of oscillation ( $f_{max}$ ) and

the transistor breakdown voltage. The impact of these FOMs on the millimeter wave components, including the power amplifier, is discussed in this section.

#### 2.3.4.1 Frequency of Transition

$f_t$  is defined as the frequency where the absolute value of the output hybrid parameter referenced from the input port becomes unity and is therefore the maximum frequency where current gain is possible. It is highly dependent on sizing and bias conditions, resistive losses, especially the series gate resistance and layout parasitics. Practically, the measured scatter parameter data is transformed into hybrid parameter data using the transform below. The definitions of the scatter parameters are taken from [31].

$$H_{21} = \frac{-2S_{21}}{(1 - S_{11})(1 + S_{22}) + S_{21}S_{12}}.$$

Equation 1

#### Investigating Frequency of Transition

Circuit models were used to simulate  $f_t$  for the various NMOS transistor parameters. Firstly a voltage supply voltage,  $V_{DD}$ , needs to be chosen. This was investigated using a voltage sweep from 0V to 1.6V, the maximum drain voltage for the NMOS transistor. Feedback is used to bias the gate, with the circuit displayed in Figure 9.

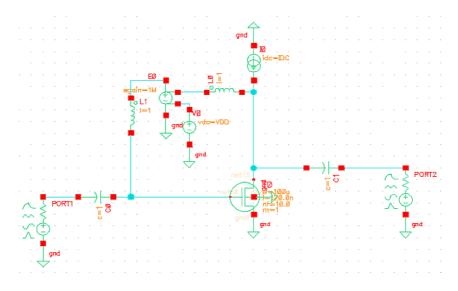

Figure 9 – NFET Characterisation Circuit

A VDD of 1.5-V was chosen as the DC supply voltage as it is 100mV below the maximum voltage allowing a margin for safety. In practice, this safety margin may have to change depending on the variation in the voltage source. The gate bias feedback voltage was 950mV. Multiple current densities, finger sizes and total device widths contained, including all combinations, were simulated and these are contained in Table I.

| Variable              | Values                                                                         |

|-----------------------|--------------------------------------------------------------------------------|

| Total Device Width(m) | 20u, 40u, 60u, 80u, 100u,120u                                                  |

| Current Density(A/m)  | 20, 40, 60, 80, 100, 120, 140, 160, 180, 200, 220, 240, 260, 280, 300, 320     |

| Finger Width          | 0.5u, 1u, 1.5u, 2u, 2.5u, 3u, 3.5u, 4u, 4.5u, 5u, 5.5u, 6u, 6.5u, 7u, 7.5u, 8u |

Table I – Swept device parameters for NMOS transistor

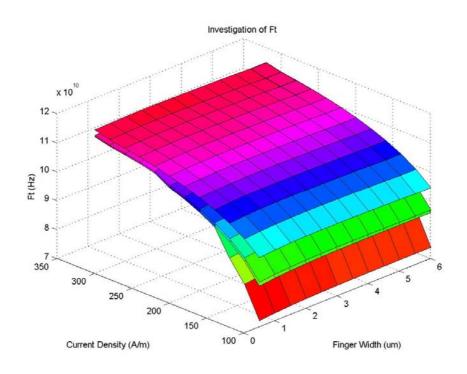

Figure 10 – Simulations of  $f_t$  of NMOS Transistor [94]

The output of the NFET characterisation circuit is shown in Figure 10 with the total device width shown as layers from the lower  $20\mu m$  to the upper  $120\mu m$ . These results highlight the relationship between  $f_t$ , current density, finger width and total width. Clearly visible on the graph is the invariance of  $f_t$  to finger width which is consistent with MOSFET theory stated as *Equation 2* and *Equation 3*.

$$I_{D,MAX} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2$$

Equation 2

$$f_t = \frac{g_m}{2\pi (C_{gs} + C_{gd})}$$

Equation 3

It is also evident that  $f_t$  is proportional to current density and inversely proportional to total device width and a device with  $f_t$  greater than 100 GHz is achievable.

#### 2.3.4.2 Maximum Frequency of Oscillation

The maximum frequency of oscillation  $(f_{max})$  is probably the most important consideration for the design of the power amplifier. Defined as the frequency at which Mason's Unilateral Gain, defined below, is unity [87] it marks the frequency point where the transistor moves from an active device to a passive one. At frequencies higher than  $f_{max}$  the transistor becomes a passive device and gain is impossible. The value of  $f_{max}$  is highly dependent on sizing and bias conditions, resistive losses and layout parasitics. For narrowband tuned amplifiers where capacitance is resonated out,  $f_{max}$  is the better metric for the active device frequency characteristics.

The unilateral gain defined by Mason is the most common design criteria for transistors because the gain is invariant to the common terminal for an active device. To achieve unilateral gain for a two port network  $S_{11}$ ,  $S_{21}$  and  $S_{22}$  must be reduced to zero, Equation 4, by lossless feedback and lossless matching.

$$S_{u} = \begin{bmatrix} 0 & 0 \\ U^{\frac{1}{2}} \angle \theta_{u} & 0 \end{bmatrix}$$

Equation 4

Substitution in the S-parameter matrix allows the calculation of U by Equation 5 [87],

$$U = \frac{\left| \frac{S_{21}}{S_{12}} - 1 \right|^2}{2 \left[ k \left| \frac{S_{21}}{S_{12}} \right| - \text{Re} \left[ \frac{S_{21}}{S_{12}} \right] \right]}$$

Equation 5

Solving these equations for MOSFETs the  $f_{max}$  may be expressed relative to the devices inherent properties,

$$f_{\text{max}} = \frac{g_m}{2\pi (C_{gs} + C_{gd})} \sqrt{\frac{1}{g_{ds} (R_G + R_S) + \frac{g_m R_G C_{GD}}{(C_{gs} + C_{gd})}}}.$$

Equation 6

Investigating Maximum Frequency of Oscillation

$f_{\text{max}}$  can be shown theoretically to be independent of the number of fingers of a transistor. Therefore to optimize a multi-finger transistor it is sufficient to optimize the layout of a single finger transistor to reduce the resistive losses the most significant being gate, source and drain resistances.

By using multiple narrow finger widths the gate resistance becomes negligible with the disadvantage of an increased gate capacitance which can be addressed with matching networks. The advantage of a negligible gate resistance is that  $f_{\text{max}}$  will be primarily determined be the source and gate resistances.

The same NFET characterisation circuit, shown in Figure 9, with the same biasing conditions and a swept of the same parameters, shown in Table I was used to investigate  $f_{\text{max}}$ .

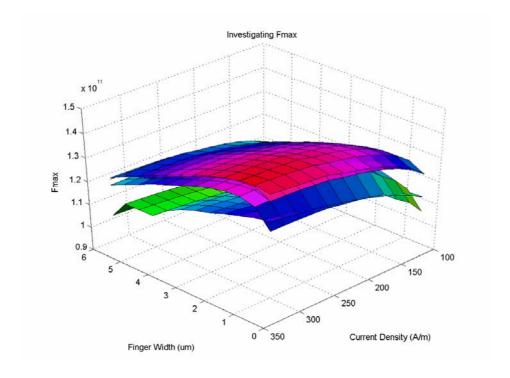

Figure 11 shows the results of the simulations for finger width, number of fingers and total width. From these simulations the following can be concluded:

$f_{\text{MAX}}$  increases with the total width of the transistor. This is visible as the equal total device width planes increase with the total width of the transistor, from lowest through to highest in order, 30um, 60um, 90um and then 120um. It is clear that increasing the total width of the transistor from 90um to 120u has limited affect in the  $f_{\text{MAX}}$  of the transistor.

Decreasing the finger size of the transistor does not exclusively increase  $f_{\text{MAX}}$ . Instead, at finger sizes less than 2.5um reducing the finger size may reduce  $f_{\text{MAX}}$ , this is clearly the case for a transistor with total width of 60um.

The transistor device benefits from being biased into strong inversion for optimal operation in millimeter-wave frequencies. For this reason a current density greater than 250 A/m is preferred.

Figure 11 – Simulations of  $f_{max}$  of NMOS Transistor

#### 2.3.4.3 Breakdown Voltage

The third critical figure of merit affecting power amplifiers performance is breakdown voltage. Breakdown voltage directly influences the magnitude of the voltage swing of the device. The time-dependent dielectric breakdown (TDDB) is the most significant limitation on the voltage range of a MOSFET. The TDDB is a function of hot carrier effects, gate oxide breakdown, snapback breakdown and junction breakdown [41]. This process damages the silicon-oxide interface and reduces the threshold voltage of the device over time.

The recommended device limitations are set by the foundry and based on DC or transient reliability test at the minimum channel lengths. It has been stipulated [62] that further investigation may relax the conservative limits on the supply voltage but this is outside the scope of this thesis. For further information the reader is directed to [62], [65], [87].

#### 2.4 Passives

Detailed analysis of a process would not be complete without considering the implementation of passives on a process, especially as the area of passive components on a RF transceiver is far larger then the actives. This section will discuss the information of millimetre wave passives on CMOS.

#### 2.4.1 Resistors

Resistors are used sparingly in millimetre-wave CMOS design. Two examples are biasing circuits employing resistors to provide isolation, and amplifiers commonly utilising resistors to stabilize the circuit. Resistors available for use in the CMOS process include doped and undoped polysilicon resistors, diffused substrate resistors, and BEOL precision thin film resistors. The latter is only available with the purchase of an extra mask and thus is generally undesirable for use.

#### 2.4.2 Inductors

Millimetre wave inductors on CMOS are utilised extensively to tune out parasitic capacitances exhibited by active devices. At millimetre waves inductances are predominantly realised by short sections of transmission line. Distributed transmission line element inductors exhibit reduced process variation and improved isolation when compared to their lumped equivalents. With well characterised transmission lines simply variation of the length will produce a required inductance (within limits). In reality the length, width and separation of the signal and return paths needs to be investigated to ensure correct operation.

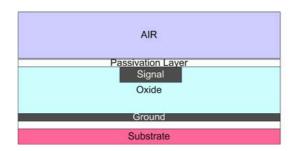

The two commonly implemented transmission lines are shown below. Figure 12 shows the cross section of a microstrip transmission line typically implemented using one of the top layers as the signal line and one of the bottom most layers as the return path. The bottom ground plane acts as a shield reducing the signal substrate loss. Figure 13 shows the cross section of a coplanar waveguide typically implemented using one of the top layers with small conduction loss and the ability to implement wider metal paths. The ability to finely control the spacing of the return paths facilitates ease of tuning of the desired inductance and resistance properties.

Figure 12 – Cross section of a microstrip transmission line.

Figure 13 – Cross section of a coplanar waveguide transmission line.

#### 2.4.3 Capacitors

In millimetre wave design capacitors are used as DC blocking, AC coupling and (rarely) for impedance matching networks. The CMOS process facilitates a number of lumped element capacitors, the MOM (metal-oxide-metal) and the MIM (metal-insulator-metal), the latter requiring an extra mask set to produce, and also the realisation of a capacitor with distributed element transmission lines similar to those discussed for inductors.

#### 2.5 CMOS Future Trends

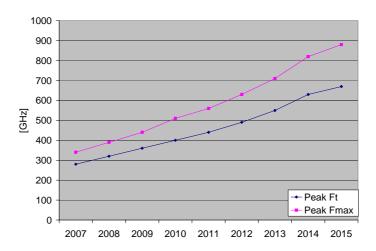

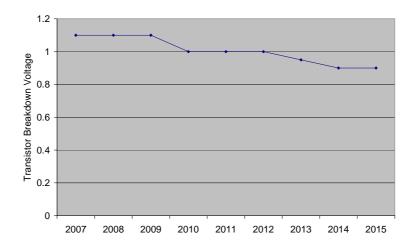

Two strong trends are predicted [40] that will effect the implementation of millimetre wave CMOS devices in the future. Figure 14 shows the increase in the performance of CMOS  $f_{max}$  and  $f_t$  that is predicted in the coming decade. This trend allows for more gain and faster switch of active device, facilitating reduced difficulty in achieving gain at millimetre wave frequencies. Figure 15 shows the decrease in supply voltage that is predicted in the coming decade. This trend increases the difficulty in designing circuits with sufficient power handling capabilities and will predictably lead creative solutions that utilise greater currents and less voltage.

Figure 14 – Industry [40] estimates of future  $f_{max}$  and  $f_t$  transistor trends.

Figure 15 – Industry [40] estimates of future transistor breakdown voltage trends.

# 2.6 Conclusion

This chapter has presented the motivation for the use of Silicon Complementary Metal–Oxide–Semiconductor (CMOS) technology and highlighted the strengths and weaknesses of this selection, discussed implementation of the actives and passives and the impact of future technology advances.

# Chapter 3

# Fundamentals of Radio Frequency Power Amplifier Design

#### 3.1 Introduction

The role of the power amplifier circuit is to generate significant output power at RF frequencies by converting DC input power. Each transmitter contains at least one power amplifier but they are also found on systems as diverse as signal generators, frequency converters, microwave heaters, and DC-to-DC converters amongst others. This chapter introduces some fundamental concepts required for the design and implementation of a power amplifier in a radio frequency (RF) system, including an overview of the concepts of classes of PA, high frequency amplifier techniques, high power amplifier techniques, matching networks, linearity and efficiency will be discussed.

#### 3.2 Transceiver Architecture

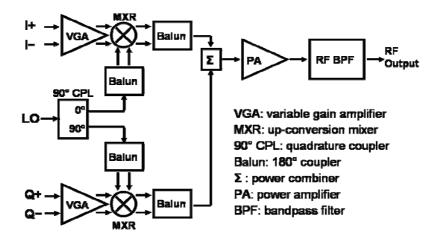

Figure 16 shows a typical homodyne front-end architecture for a RF transmitter. The PA is located in the transmit path after the mixers and before the band-pass filter (BPF) and the RF Output, typically an antenna. Variable gain amplifiers (VGA) are used to provide sufficient input signal power to the mixers.

For completeness Figure 17 shows a typical homodyne receiver architecture. The RF input, typically from an antenna, is passed through a Low Noise Amplifier (LNA), divider, mixer and output to base-band.

Figure 18 shows a micrograph of a single die 60-GHz CMOS homodyne transceiver with architecture described in Figure 16 and Figure 17. Additionally included on-die is the phase lock loop (PLL), serial peripheral interface (SPI), and test structures. The SPI consists of an adaptive biasing circuit which includes a digital control and timing interface (DCTI), DACs and ADCs. The adaptive biasing circuit is utilised to neutralise the degradation in performance that occurs in the transceiver due to the fabrication process variations

(parasitics), temperature variations and voltage variations. The PLL circuit is utilized to produce an operating frequency to match a stable reference signal.

Figure 16 – Typical Homodyne Transmitter Architecture [53]

Figure 17 – Typical Homodyne Receiver Architecture [53]

# 3.3 Classes of Power Amplifiers

RF power amplifiers are generally divided into classes. The most common of these classes are denoted A, B, C, D, E, and F with additional classes occasionally specified in literature. The class-A power amplifier is a version of the standard small-signal linear amplifier with increased power handling capability, whilst the other classes employ various wave-shaping, non-linear and switching techniques to achieve the required performance. Originally, class specified the bias conditions but these classes grew to include variations from the "classic"

theory of the class-A, AB, B, C amplifiers. This section will discuss the topologies, biasing, power handling capability, linearity and efficiency of the power amplifier classes.

Figure 18 – Single Chip 60GHz CMOS Transceiver Micrograph

## 3.3.1 Class-A, AB, B, and C Power Amplifiers

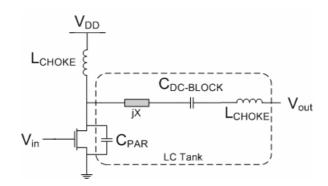

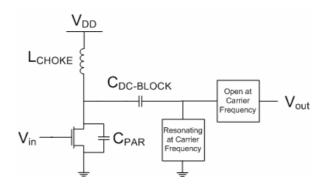

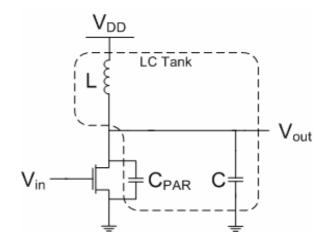

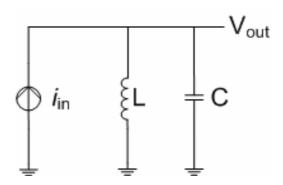

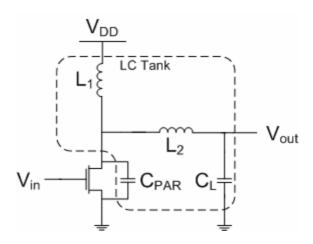

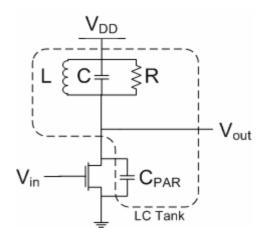

These four amplifiers are architecturally similar and are distinguished most significantly by biasing conditions; all four will be discussed using the architecture shown in Figure 19. In this generic model, the output  $V_{OUT}$  is assumed to be connected to the load into which the power is to be delivered, usually a transmit / receive switch, band pass filter or an antenna. The parasitic capacitance of the transistor,  $C_{PAR}$  and the output impedance,  $Z_{OUT}$ , with

superficial input from the  $L_{CHOKE}$  and  $C_{DC-BLOCK}$ , form an LC tank ideally resonating at the centre frequency of the channel.  $L_{CHOKE}$  is a large inductor and serves to supply DC power to the MOSFET drain and the  $C_{CHOKE}$  is a large capacitor and serves as a DC block / AC signal pass.

Figure 19 – Genetic Power Amplifier Architecture

In class-A the power amplifier is a scaled-up small-signal amplifier. It is the most linear of the power amplifiers as the output signal is ideally an amplified version of the input signal with minimal distortion, however this results in low efficiency. The quiescent current is large allowing operation wholly in the pentode (saturation) region with the active device operating as a current source controlled by the input current. A significant difference between the class-A power amplifier and the small signal amplifier is that the signal currents in the power amplifier are a substantial proportion of the biasing levels, with the LC tank supplying the reservoir of power that alleviates the potential for distortion under normal operating conditions. Therefore Class-A power amplifiers are typically used in applications requiring high gain, linearity, and high frequency operation, such as those described in this thesis.

In an effort to improve the efficiency of the class-A power amplifier at the expense of linearity, the gate bias of the amplifier is reduced causing the input RF signal to "turn on" and "turn off" the active device, therefore reducing the amplifier conduction duty cycle, the percentage of the waveform of the input signal that is amplified, and reducing power. Biasing the amplifier with low quiescent current allows the radio frequency alternating current signal to turn on the active device. Between 100% and 50% conduction duty cycle

the power amplifier is biased in class-AB. At 50% conduction duty cycle the power amplifier is biased at the threshold of conduction so ideally the quiescent current is zero and this is defined as class-B operation and at a conduction duty cycle less than 50% it is biased in class-C.

Figure 20 – Class D Architecture

#### 3.3.2 Class-D Power Amplifiers

The class-D power amplifier shown in Figure 20, employs the active device as a switch instead of a controlled current source. As a switch ideally dissipates no power, as there is no current passing through it when it is in the off state or no voltage across it when it is in the on state, therefore if it switches between these states in zero time the efficiency ideally approaches 100%. The class-D amplifier cannot normally provide linear modulation and as a switch-mode amplifier operates well below  $f_t$ . This amplifier suffers from losses due to saturation, finite transistor switching speed causing the active device to remain operating in the active regions while conducting current, and the charging and discharging of the drain capacitance.

## 3.3.3 Class-E Power Amplifiers

The class-E power amplifier shown in Figure 21 is another class of amplifier employing switched-mode operation. A high-order network is used to absorb the parasitics of the active devices, eliminating the losses associated with charging of the drain capacitances (as occur in class-D), with enough degrees of freedom to allow the shaping of the voltage so that it is possible to have zero drain current and zero voltage at turn on and thus an

efficiency approaching 100%. The drawbacks are higher complexity and a reduced power handling capacity.

Figure 21 – Class E Architecture

## 3.3.4 Class-F and Inverse Class-F Power Amplifiers

The class-F and inverse class-F power amplifier is another amplifier class employing switch-mode operation. The concept of exploring harmonic resonating terminations to shape the current and voltage waveforms used in class-E amplifiers is extended by the use of extra resonating networks and as a result the amplifier has increased efficiency. In a class-F amplifier the voltage waveform consists of one or multiple odd harmonics, and the current waveform consists of one or multiple even harmonics. Conversely, the inverse class-F amplifier current waveform consists of one or multiple odd harmonics, and the voltage waveform consists of one or multiple even harmonics.

#### 3.3.5 Class-G, Class-H Power Amplifiers

Class-G and class-H amplifiers are a more efficient version of the classic, transconductance power amplifiers. The class-G amplifier uses discrete "rail switching" to decrease power consumption and thus increase efficiency. The amplifier employs a number of power rails to increase the supply as required.

The class-H amplifier extends the class-G amplifiers discrete "rail switching" to a continuous versions supplying sufficient voltage for optimum efficiency at all input voltage levels, otherwise known as envelope tracking.

Figure 22 – Class F Architecture

#### 3.3.6 Hybrid Class Power Amplifier

Several hybrid power amplifier classes have been proposed to deal with some of the disadvantages of the single class power amplifiers. These hybrid class amplifiers include; the class-BD power amplifier with a linear transfer characteristic, higher efficiency and with the same peak output power as a class-B [66]; the class-EF power amplifier incorporates the transistor parasitics but also shapes the output harmonics to achieve the desired current and voltage output waveforms [43].

## 3.4 High Frequency Amplifier Techniques

Designing amplifiers for operation at high-frequencies, operating the devise close to their inherent limitations, requires more advanced considerations a designing amplifiers at lower frequencies. Device parasitics are more pronounced at high frequencies, gain is harder to achieve, and the difficulty in designing high quality passives are a few of the challenges that impose serious constraints on circuit performance.

Several techniques used to enable high frequency amplifier design are discussed below.

#### 3.4.1 Shunt Peaked Amplifiers

For a purely resistively loaded common-source amplifier the gain is proportional to  $g_m R_L$ . When a capacitance load is added the gain will reduce with frequency as the impedance reduces, Equation 7. This capacitive load may be the input capacitance of another transistor amplifier stage which is highly useful if cascading of amplifier stages is required.

$$Z(s) = R \parallel \frac{1}{sC} = \frac{R}{sRC + 1}$$

Equation 7

Adding an inductive load, a zero in series, causes the impedance to increases with frequency which offsets the decreasing impedance of the capacitance. This will produce an impendence that varies less over a broader frequency range then the original network.

Figure 23 – Shunt Peaked Amplifier

Figure 24 – Equivalent Model of the Shunt Peaked Amplifier

From Figure 24 the impedance of the RLC network may be written as

$$Z(s) = (sL + R) \parallel \frac{1}{sC} = \frac{R[s(\frac{L}{R}) + 1]}{s^2LC + sRC + 1}$$

Equation 8

In contrast with the RC case there now is a quadratic term in the denominator that now aids in increasing the bandwidth. This can increase the -3 dB bandwidth by a maximum of the square root of 2 [50].

Figure 25 – Shunt and series peaked amplifier

## 3.4.2 Shunt and Series Peaked Amplifier

Shunt peaking may be augmented by additionally separating the load capacitance from the output capacitance of the device. Figure 25 shows the result if an inductor is used to perform the separation, this is a combination of shunt and series peaking.

This leads to only a slightly larger bandwidth then the shunt case. Shunt Peaked amplification can lead to shunt and double series peaking, then to T-Coil bandwidth enhancement and then eventually to negative feedback [31], [50].

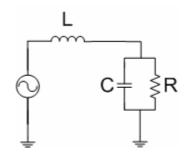

Figure 26 – Amplifier with Tuned Load

## 3.4.3 Tuned Amplifiers

Tuned amplifiers are used to extensively in communications circuits both to provide a high level of amplification within the channel and to filter unwanted frequencies outside the channel. Furthermore the power required to obtain the high gain can be considerably less than for broadband implementation.

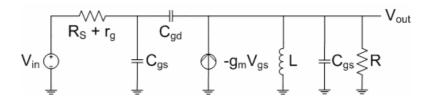

Using the model for the amplifier with tuned load depicted in Figure 26, the input and output admittances can be calculated. To do this the value of  $V_{gs}$  will be fixed to make the mathematics easier, as it controls the value of the current source.

Figure 27 – Amplifier with Tuned Load Model

From the amplifier with tuned load model the capacitance of the output port of the transistor is given by, essentially Figure 27 with the RLC tank removed.

$$C_{eq} = C_{gd}[1 + g_m(R_S + r_g)]$$

Equation 9

This is essentially the Miller Effect viewed from the output port, and will shift the resonant frequency downward. This shift can be compensated by increasing the inductance of the RLC tank.

Considering the input admittance next, ignoring input and gate-source impedances the following equation is produced. The approximation follows if  $y_L >> y_{RLC}$ .

$$y_{in} = \frac{y_{Cgd} y_{RLC}}{y_{Cgd} + y_{RLC}} + \frac{g_m y_{Cgd}}{y_{Cgd} + y_{RLC}}$$

$$\approx y_{Cgd} + \frac{g_m y_{Cgd}}{y_{RLC}}$$

Equation 10

This equation is problematic as  $y_{in}$  can now have a negative real part due to  $C_{gd}$ . This would be ideal if oscillation was the goal of the circuit but unfortunately it is not. Turning the input, as is required for the PA, will only increase the circuits tendency to oscillate and not be a power amplifier. More on oscillators can be found in [31],[50] but will not be covered here as it is outside the scope of this report, though tuning still has an important role to play in the design of the PA and will be further discussed below. But first we have to do something about  $C_{ord}$ .

## 3.4.4 Neutralization and Unilateralization

The magnitude of  $C_{gd}$  is a problem because the input port is coupled with the output port essentially allowing feedback between them. Removing or reducing this coupling via unilateralization reduces the potential for instability, detuning and neutralization of the Miller effect. This can be achieved in various ways; one example is the use of a commongate stage creating the Cascode Amplifier, Figure 28. In this configuration the input signal drives the gate of the common-source device, whilst the gate of the common-gate device is grounded exhibiting a low input resistance to the common-source device and reducing the voltage gain, and thus Miller Effect of the common-source device. The high resistance of the output of the common-gate device produces voltage gain.

Figure 28 – Cascode Amplifier with Tuned Load

## 3.4.5 Cascading

When insufficient unilateral power gain is available cascading of stages is required. This is most often achieved with an input stage, driver stage and output stage with input, output and interstage matching networks.

Figure 29 – Cascade Radio Architecture

Cascading stages will have a negative impact on bandwidth but allows for increased gain is impossible without cascading. This shrinkage is inversely proportional to the inverse square root of the number of stages.

## 3.5 High Power Amplifier Techniques

The power amplifier designer is always struggling for methods to supply more output power. This is especially evident when using the CMOS process, as it was not designed for power handling capability. Relying on the Power Law, P = vi, it is obvious that to increase the output power either the output voltage, output current or both need to be increased. This section will discuss the techniques used in literature to increase the output voltage and the output current.

#### 3.5.1 Voltage Combining

Combining voltage by placing transistors in series allows several devices to contribute to the output voltage and thus increase the output power. Combining voltage requires careful consideration of device breakdown voltages. Exceeding the device breakdown voltages will result in damage to the transistor and a reduction in performance. This section will introduce the theory behind voltage combining with the design of several voltage combiner topologies discussed.

#### 3.5.1.1 Cascode Topology

The cascode topology, Figure 28, covered previously in section 3.4.4 as a method for increasing neutralization and unilateralization of high frequency amplifiers, especially

helping to reduce the unwanted capacitive feedback of the Miller Effect. The cascode is a two-stage amplifier consists of a common-source device with a common-gate device connected to the drain. The gate of the common-source device is driven by the input signal, with the gate of the common-gate obviously AC grounded.

The cascode topology aids the power amplifier designer by allowing the circuit to sustain higher voltage before breakdown then would be possible with only one stage. Care with biasing is required to evenly share the stress caused by the higher voltage between both devices, and thus not allowing one of the devices to breakdown.

Research into several techniques to overcome the device stress of the cascode under high voltages has been presented. Research into using think-oxide devices for the common-gate device of the cascode, usually the more stressed device, to allow higher device output swing is presented in [100]. This work is not applicable for high frequency operation as thick oxide devices have a poor high frequency response and are therefore not a suitable solution for a designer looking for high frequency operation. Research into a self biased cascode topology has been presented in [80]. In this work the common-gate DC bias is dynamically biased at the same level as the output of the power amplifier. This theoretically relaxes the restriction due to the hot-carrier degradation and allows an increased voltage supply without shortening of the devices lifespan.

The disadvantages of the cascode topology include potential instability especially if an AC signal is present at the gate of the common-gate device, and possible power loss in the common-gate device. Both these issues can be overcome but require careful attention by the designer.

#### 3.5.1.2 Totem-Pole Topology

The totem-pole amplifier, shown in Figure 30, extends the concept of the cascode amplifier by summing voltages over multiple devices in series. It also uses a self-biasing feedback ladder network to bias the common-gate devices, a similar to but extended version of the self-biasing feedback of [80]. By allowing the voltage to be distributed over multiple devices, no single device needs to exceed breakdown, and the sum of all the devices will

exceed the breakdown of a single device allowing a higher supply voltage and a higher voltage swing at the output.

Figure 30 – Totem-Pole Architecture

For high frequency RF operation the propagation delay in the bias network severely hampers the usefulness of the totem-pole amplifier. The bias levels of the gate of the common-gate devices will not be synchronised, causing phase and amplitude distortion.

#### 3.5.1.3 Stacked Transistor Amplifier Topology

The stacked transistor amplifier, shown in Figure 31 is a modified totem-pole amplifier that addresses the significant drawback of the frequency range of the amplifier. Recalling, that the poor frequency response of the totem-pole was caused by the resistive biasing network, [57] proposes replacing this network with transformer coupling.

#### 3.5.2 Current Combining

Combining current by placing transistors in parallel allows several devices to contribute to the output current and thus increase the output power. Combining power requires careful consideration of reflections and distortion from poor matching. To successfully match networks and overcome this problem power combiners are required, either in a distributed or lumped component approach. This section will introduce the theory behind current combining with the design of current combiners discussed including transformer based and transmission-line based combiners.

Figure 31 – Stacked Transistor Architecture

## 3.5.2.1 Transmission-Line Power Combining

As the operating frequency of transceivers moves into the millimetre wave spectrum the size of transmission lines scale inversely. This facilitates the use of on-chip transmission line based combining. Slow-wave structures have also been presented [75], [62] that improve the quality factor and reduce the dimensions of transmission lines. Lumped equivalent circuits have also been used in the low GHz range to synthesise transmission-line power combining circuits. In this section the most prominent power combining structures will be discussed.

Figure 32 – Wilkinson Power combiner

## Wilkinson and Corporate Power Combining

The Wilkinson power combiner [99] shown in Figure 32 ideally allows lossless power combining when the output ports are matched, with only the reflected power dissipated.

Figure 33 – Lumped Element Wilkinson Power combiner

In the centimetre-wavelength range the size of the transmission lines hinder the application of the distributed element combiner and power amplifier designers have instead focussed on lumped element equivalent implementations as shown in Figure 33. As the frequency increases into the millimetre-wavelength range transmission lines and distributed elements become more practical.

Figure 34 – Corporate Power Combiner

A corporate power combiner extends the Wilkinson power combiner by employing several stages of combiner into the one larger structure, shown in Figure 34. The corporate combiner similarly also suffers at centimetre-wavelength frequencies to the large die area required for distributed implementation, but is again more practical at higher millimetre-

wave frequency although the author cannot find an example of this technique being implemented at these frequencies. Lumped implementations are also problematic due to the complexity of the networks required.

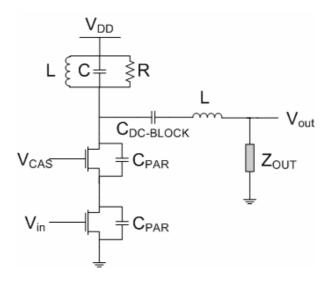

#### Doherty Power Amplifier Combiner

The Doherty amplifier uses multiple amplifiers to boost average efficiency, with each amplifier contributing to the output power only over some subset of the overall power range, similar to the concept of a turbocharger. The concept first proposed by Doherty [21], used two amplifiers, a main and an auxiliary which will be disused below.

Figure 35 – Two amplifier Doherty Amplifier Architecture [95]

The Doherty amplifier consists a quarter wavelength,  $\lambda/4$ , input transmission line network to split the input signal between the two amplifiers and a quarter wavelength transmission-line connecting the input to the main amplifier cell with characteristic impedance of  $Z_0$ , and a quarter wavelength transmission line with characteristic impedance of  $Z_0/\sqrt{2}$  connecting the inputs of the main amplifier cell with the auxiliary amplifier cell. A second quarter wavelength transmission line network is used to combine the outputs of the two amplifiers, with the output transmission line connection used to compensate for the phase shift of the splitter and combining the output currents in phase. The main amplifier is biased with a larger conduction angle compared to the auxiliary amplifier with the main amplifier biased in class AB and class C. The result of this biasing is for a high input signal both amplifiers are at their maximum output power each amplifier and will see an equal load and as the power of the input signal is reduced the auxiliary amplifier drain current turns off, leaving

only the main amplifier is active. This technique, termed the active load-pull technique, causes the reactance of the load to vary by combining current from a second in-phase source.

The operation of the Doherty amplifier, model shown in Figure 36, can be approximately analysed using three regions of operation, a high power region where both amplifiers are fully on, 0 dB backoff point, a middle region where the auxiliary amplifier contributes a proportion of its maximum output power, 0 - 6 dB backoff, and a low power region where the auxiliary amplifier is has insufficient signal power to turn on, greater then 6 dB backoff. The details relevant to this thesis are presented below; if the reader is interested a more detailed explanation is found in [10].

Figure 36 – Doherty Amplifier output model

Letting each of these regions correspond to a  $\xi$  value between 0 and 1 corresponding to the proportion of its maximal output the auxiliary amplifier is producing allows RF currents from the current sources to be expressed in the form,

$$I_1 = \frac{I_{MAX}}{4}[1+\xi],$$

Equation 11

$$I_2 = \frac{I_{MAX}}{2} \xi.$$

Equation 12

The effective resistances,  $Z_{1T}$  and  $Z_2$ , can now be expressed in the form,

$$Z_{1T} = R_L \left( 1 + \frac{I_2}{I_{1T}} \right),$$

Equation 13

$$Z_2 = R_L \left( 1 + \frac{I_{1T}}{I_2} \right).$$

Equation 14

With the relationship between the input and output voltages and currents of the quarterwave transmission line expressed as,

$$\begin{aligned} V_{1T}I_{1T} &= V_1I_1 \\ Z_0^2 &= \left(\frac{V_{1T}}{I_{1T}}\right)\left(\frac{V_1}{I_1}\right), \end{aligned} \qquad Equation 15$$

$$I_{1T} &= \frac{V_1}{Z_T}$$

Substitution of  $I_{1T}$  in the expression for  $Z_{1T}$ , gives

$$Z_{1T} = R_L \left( 1 + \frac{I_2 Z_T}{V_1} \right).$$

Equation 16

Solving for the impedances at the output devices,

$$Z_{1} = \frac{Z_{T}^{2}}{Z_{1T}}$$

$$= \frac{Z_{T}^{2}}{R_{L}\left(1 + \frac{I_{2}}{I_{1T}}\right)}$$

$$Z_{2} = R_{L}\left(1 + \frac{I_{1T}}{I_{2}}\right)$$

Equation 17

Output resistance of the load for the three regions of operation can now be calculated, these highlight the change in output impedance seen from the main amplifier;

For the high power region where both amplifiers are fully on, thus the 0 dB backoff point,

$$I_{1T} = I_2$$

$$Z_1 = \frac{{Z_T}^2}{2R_L}.$$

Equation 18

$$Z_2 = 2R_L$$

For the middle region where the auxiliary amplifier contributes a proportion of its maximum output power, thus 0-6 dB backoff,

$$Z_{1} = \frac{{Z_{T}}^{2}}{R_{L} \left(1 + \frac{I_{2}}{I_{1T}}\right)}.$$

$$Equation 19$$

$$Z_{2} = R_{L} \left(1 + \frac{I_{2}}{I_{1T}}\right)$$

For the third state, a low power region where the auxiliary amplifier is has insufficient signal power to turn on, thus greater then 6 dB backoff,

$$I_2 = 0$$

$$Z_1 = \frac{{Z_T}^2}{R_L}.$$

Equation 20

$$Z_2 = \infty$$

Finally, solving for V<sub>1</sub>,

$$V_{1} = \left(\frac{Z_{T}}{2R_{L}}\right) \left(\frac{I_{MAX}}{2}\right) \left(Z_{T} + \zeta \left(Z_{T} - \frac{R_{L}}{2}\right)\right).$$

Equation 21